AMD is enjoying Intel’s loss of momentum to get back on track. With the Epyc server chips, it breaks the Xeon hegemony of Intel and Epyc Rome promises a big step forward to reassure doubters.

AMD has revealed new details about Epyc Rome (Zen 2 architecture), the new server chips that are baked for the first time at 7 nm. With the first Epyc (Zen 1 architecture) chips, AMD put itself strongly on the map from scratch, but confirmation is needed and a roadmap to convince companies to invest in AMD. Epyc Rome confirms and exceeds expectations with a promising first unveiling and a look at the Epyc roadmap.

According to AMD CTO Mark Papermaster, the second generation of Epyc chips will contain a significant improvement on the original design. Floating point throughput is doubled thanks to 256-bit AVX2 registers. Load/Store bandwidth is also doubled according to Extremetech. The dispatch and retire bandwidth increases, as does the micro-op cache.

Doubling

All these improvements ensure that the Epyc performance is well on its way to the top. The only thing that is not certain is the decrease in clock speed when the AVX2 is running. Intel has to do this with their Xeon chips.

Read this: Intel must aggressively compete AMD in the server market

AMD offers PCIe 4.0 support for Epyc Rome but also supports the first generation Epyc chipsets and the next generation Milan Epyc 3 chips. This means that the cpus can use both PCIe 3.0 and 4.0, depending on the platform in question.

The number of cores has not yet been juggled, but AMD consistently speaks of a doubling of the processing power. Presumably the new Epyc 2 chips will have up to 64 cores, compared to 32 cores of the current series.

New design

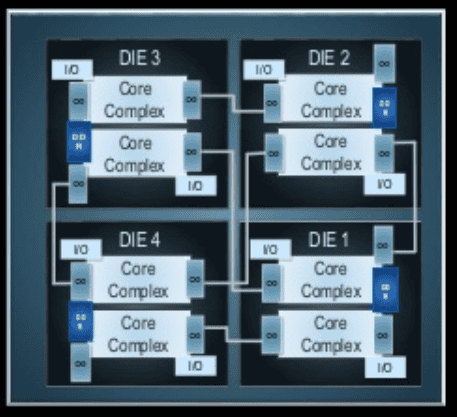

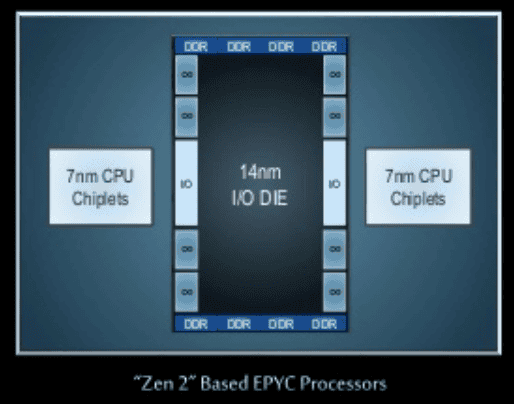

The biggest innovation is the implementation of the Infinity Fabric and memory controllers with which the different dies on a chip communicate with each other. In the first generation Epyc each one had its own memory controllers, Infinity Fabric links and PCIe channels. Now AMD centralizes all this IO in a 14 nm I/O and around it are the 7 nm dies with the pure processor power. In the central I/O which are eight memory controllers, eight Infinity Fabric ports have the same number of PCIe channels.

In this way, AMD eliminates an important bottleneck present in the first generation of Epyc chips. There memory latency could occur when a core of those two needed memory from a core of those four. Now everything runs centrally and that memory latency is eliminated. At the same time, it also provides a more straightforward design for each CPU.

Anyone who becomes enthusiastic will unfortunately have to be patient for a while. AMD launches Epyc Rome sometime in 2019 without giving a more precise timing. The Zen 2 platform on which Epyc Rome is running is currently being sampled. Zen 3, the successor, builds on the step to 7 nm with refinements and optimisations and is planned for 2020. Zen 4 is in the design phase and has not yet been set a deadline.

This news article was automatically translated from Dutch to give Techzine.eu a head start. All news articles after September 1, 2019 are written in native English and NOT translated. All our background stories are written in native English as well. For more information read our launch article.