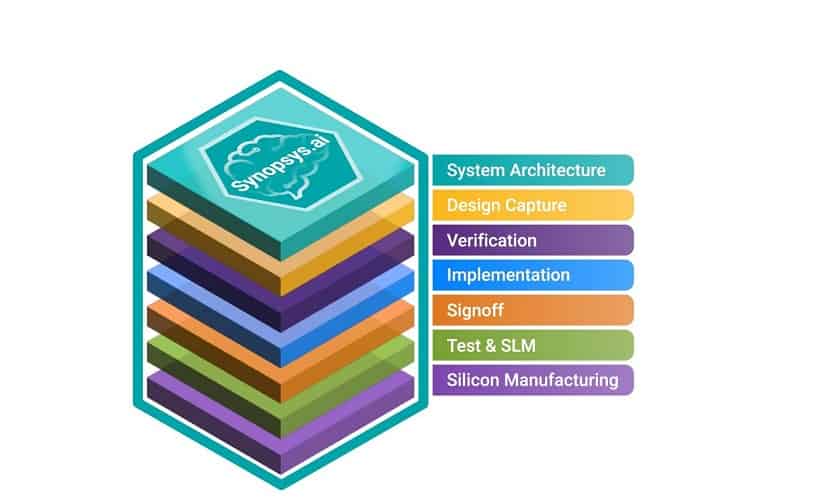

Synopsys recently released a complete EDA suite of AI tools, Synopsys.ai. This new “AI stack” helps chip manufacturers use automation to design, verify and test even more sophisticated processors.

According to Synopsis, Synopsys.ai should help chip manufacturers by applying AI in every step of the design process. From the design of the system architecture to the actual design and manufacturing process.

More specifically, the Synopsys.ai EDA suite should accelerate processor design with, initially, solutions for functional verification and testing. More functionality will be added at a later stage.

Among other things, the AI technology provided should help perform certain time-consuming iterative and also repetitive processor design tasks. These include design space exploration, verification coverage, regression analysis and test program generation. The AI tooling automates these tasks, allowing designers to focus on more important tasks such as differentiating their products and implementing new functionality faster.

Three components

The Synopsys.ai EDA suite itself consists of three components. The DSO.ai component provides automated design space exploration. This is a process for improving the power consumption, performance and size of chip designs.

The VSO.ai component should help verification specialists achieve their so-called coverage closure goals faster and discover bugs in their designs. Since digital chip designs can take many forms, it is very difficult for people to verify that they always function as they are intended. So that is where this component should help. With AI technology, this can now be handled completely automatically. This gives designers more insights on which they can take action.

The third and final component is TSO.ai. This component helps users automate the testing process. It also helps identify what defects a new processor design may have.

Successful implementations

Meanwhile, the Synopsys.ai EDA suite is already being used by nine of the ten largest global chip manufacturers, according to Synopsis. These customers would see a tenfold improvement in verification productivity and also realize lower costs for testing. The time required to design processors, as well as the cost of doing so, would also be greatly reduced.

Also read: AMD seems to be changing tack; hybrid architecture chips incoming?