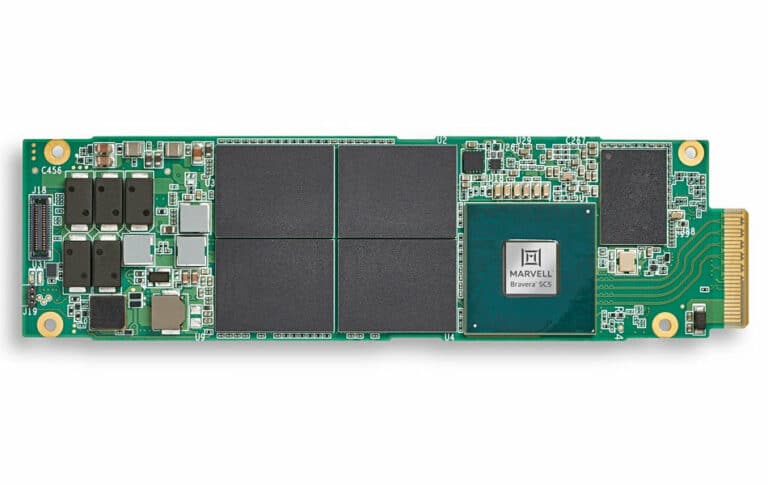

Touting enhanced security, data protection, and cloud-optimization, Marvell’s PCIe 5 SSD offers sequential read output up to to 14GB/sec.

Its performance is two times better than the PCIe 4.0 SSD controllers, and it comes in two models the MV-SS1333, which is sixteen channels, and the MV-SS1331, which is eight channels.

A striking difference from the PCIe 4.0

The performance of the brand new PCIe 5 SSD controllers is almost two times better than the PCIe 4.0 version. The sequential read goes up to 14 GB/sec, and performance goes up to two million IOPs (Input/Output Operations Per Second).

Difference between the two models

The Bravera PCIe 5 SSD controllers come in two variants, The MV-SS1333, and the MV-SS1331. Here are the differences between them:

Host Interface

They both have the same interface, which is PCIe 5.0 x4 (dual-port x2+x2 capable).

NAND Interface

The NAND interface for the MV-SS1331 is 8ch, 1600 MT/s, whereas, for the MV-SS1333, it is 16ch, 1600 MT/s.

DRAM

The DRAM is the same for both models and is DDR4-3200, LPDDR4x-4266 with ECC.

Sequential Read

The sequential read for both variants goes up to 14 GB per second.

Sequential Write

The sequential write for both variants goes up to 9 GB per second.

Random Read

The random read for both variants is two million IOPS.

Random Write

The random write for both models is 1 million IOPS.

Virtualization

Both variants have 32 virtual functions and 16 physical functions.

Max Controller Power

The max controller power for the MV-SS1331 is 8.7 W, whereas, for the MV-SS1333, it is 9.8 W.

SC5 SSD Controller – Bravera Launch Partners

Marvell has worked with hyper-scale computing users like Facebook and Microsoft Azure to develop this controller. Other launch partners include Intel, SK Hynix, AMD, and Kioxia. Marvell states that these controllers have been composed to serve as a base in data centers offering real-time applications at ultra-low latency without compromising cloud-scale capacity or being cost-intensive.

Specifications

The PCIe 5 controller can support QLC, TLC, and SLC (4/bits cell) flash, the OCP (Open Compute Project). It also has software-enabled flash, Open Channel, new ruler formats including E3, E1.L and E.1 L, NVMe 1.4b, and zoned namespaces. The controller supported two lanes in dual-port mode or four PCIe v5 lanes because the latency is lower than 6μs. Marvell also states that it has a hardware-based elastic SLA (service level agreement) enforcer.

Bravera offers FIPS compliant RoT (root of trust), multi-key revocation, and AES 256-bit encryption for security.

Sampling with potential clients has started already.