AMD is working on a ‘superprocessor’ for cloud, data center and telecom network infrastructures. The 400 Gig Adaptive SmartNIC SoC combines three accelerator technologies to provide more capabilities than current CPUs, FPGAs and SmartNICs.

The Register and HPC Wire report that Senior Fellow Jaideep Dastidar announced that AMD is developing a new generation of processors for cloud, data center and telecom network infrastructures at the Hot Chips conference. The new generation should meet increasing demand for speed, performance, capacity and bandwidth.

According to Dastidar, current CPUs are overworked because they’re used for a multitude of tasks, including networking, storage and security tasks. At the same time, the need for performance, bandwidth and resource decoupling grows.

Today’s SmartNIC, FPGAs and DPUs can help, but that isn’t enough. Workloads need higher and higher speeds, the demand for bandwidth grows, and with the advent of containers, virtualization and VMs are on the rise.

400 Gig Adaptive SmartNIC SoC

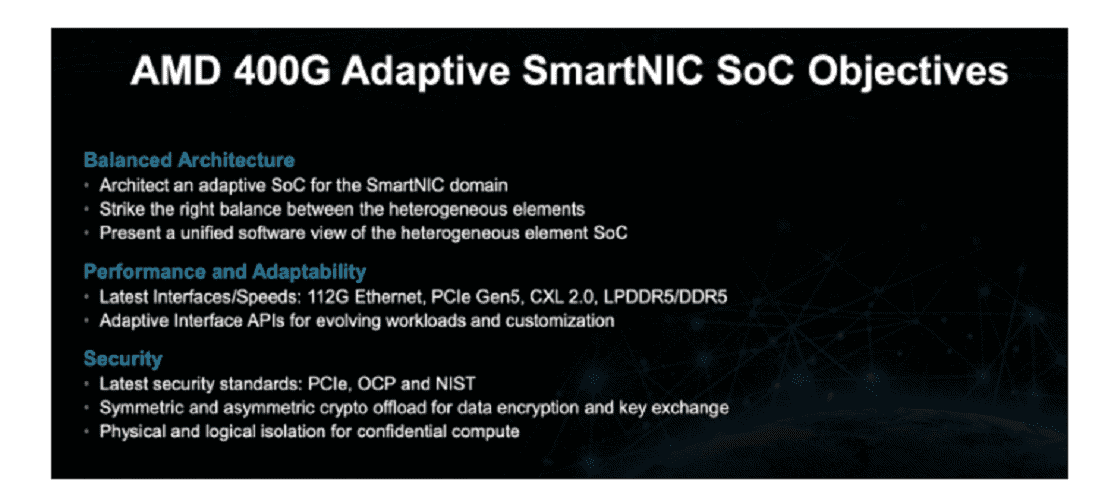

AMD wants to fill the demand for a new processor and architecture that can handle the future needs of infrastructure environments. During the conference, Jaideep Dastidar presented the 400 Gig Adaptive SmartNIC SoC in development by AMD.

The SmartNIC SoC combines the technology of FPGAs, ASICs and general compute processors in a processor application that should deliver the best possible flexibility and performance while reducing energy consumption. To this end, the chip manufacturer is deploying its own technology, as well as that of acquired FPGA player Xilinx and DPU supplier Pensando.

From a software perspective, it shouldn’t matter which component performs what function. The System-on-Chip (SoC) can perform the functionality of choice.

Workloads can however use a particular component as a preference. ASIC logic is used for what it does best: crypto offloading, DMA offloading and even complete network data-plane offloading. Customers who want to add features that don’t change often, such as certain accelerator functions, can do so again in the programmable logic available through the FPGAs. For general purpose computing power, Arm-based cores can be reused.

Other features

AMD’s upcoming 400 Gig Adaptive SmartNIC SOC features 16 A78-AE cores for high-performance workloads and four R52 cores for low-power and ‘lights-out’ operations. Memory consists of four 32GB LPDDR5 or DDR5 memory DIMMs on the SoC itself. Furthermore, the SoC features a pair of 200 Gbps interfaces and 16 lanes of PCIe 5.0 or CXL 2.0 connectivity.

The SmartNIC will be based on a TSMC 7nm process. The SoC’s release date is unknown at this time.